# NTR16CSW8 868MHz/+30dBm LoRa RF Transceiver Module

Datasheet

# **TABLE OF CONTENTS**

| 1. | NTR16CSW8 868MHz/+30dBm LoRa RF Transceiver Module in Brief | 3  |

|----|-------------------------------------------------------------|----|

| 2. | NTR16CSW8 Technical Data                                    | 7  |

| 3. | Interfacing NTR16CSW8 to Host Controller                    | 8  |

| 4. | Operational Modes                                           | 10 |

| 5. | Setting Modem, Transmitter & Receiver Parameters            | 13 |

| 6. | Module Aspects to Consider for User Application             | 17 |

| 7. | Drawings                                                    | 23 |

| 8. | Ordering Information                                        | 25 |

Revision History

References

# 1. NTR16CSW8 868MHz/+30dBm LoRa RF Transceiver Module in Brief

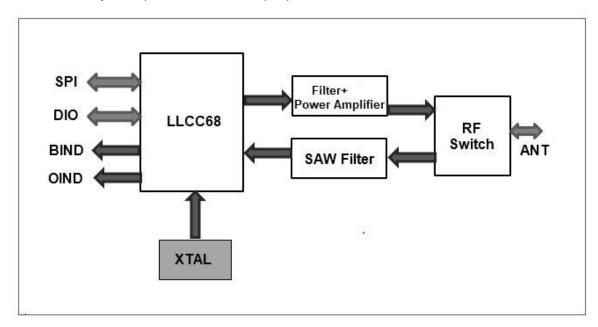

NTR16CSW8 is a small size, compact, low power and easy to use 868MHz LoRa RF Transceiver module based on Semtech LLCC68 Sub-GHz RF Transceiver IC. It supports both LoRa and G(FSK) modulations, provides radio configuration and control via the SPI interface and has up to -128dBm RF receiver sensitivity and up to +30dBm RF output power.

Fig.1 NTR16CSW8 functional blocks and interconnections

#### **Features**

- Single supply 5V operation

- Operating frequency 868MHz with LoRa and (G)FSK modems

- Up to 62.5kbps bit rate for LoRa and up to 300kps bit rate for (G)FSK

- Packet mode with data buffer, data whitening codec, FEC-Forward Error Correction

- -128dBm Receiver sensitivity, (@SF9 and LoRa BW-125kHz)

- +30dBm (1 Watt) RF output power

- High frequency stability, long range and high performance

- Low power consumption,

- 4.6mA, sleep mode <600nA (in receive mode)</li>

- 796mA (in transmit mode)

- Radio configuration and control via SPI interface

- Fully programmable frequency, modem, packet parameters and radio operational modes

- Small Size 38.90mmx28.60mm

#### **Application Areas**

- Low-cost consumer electronics applications, ISM band data communication

- Smart Building Automation

- Industrial Monitoring and Control

- Remote Control, Remote Keyless Entry, Remote AMR, Tag Reader

- Wireless Alarm and Security, Wireless Sensor Node

Fig.2 NTR16CSW8 868MHz 1Watt/+30dBm RF LoRa Transceiver Module

#### **LoRa Modulation Technique**

The NTR16CSW8 uses Semtech's patented LoRa modulation technique which combines spread spectrum modulation and forward error correction techniques to increase the range and robustness of radio communication links compared with traditional FSK or OOK based modulation. This high sensitivity, in contrast to conventional modulation techniques, permits an increase in link budget and increased immunity to in-band interference, combined with +30dBm RF power output yields industry leading link budget.

LoRa also provides significant advantages in both blocking and selectivity, solving the traditional design compromise between range, interference immunity and energy consumption. In LoRa mode the NTR16CSW8 offers ten bandwidth options as in table below.

| Signal Bandwidth | 7   | 8   | 9   |

|------------------|-----|-----|-----|

| BW_L (kHz)       | 125 | 250 | 500 |

Table 1. NTR16CSW8 LoRa Mode BW Options

The spread spectrum LoRa modulation is performed by representing each bit of payload information by multiple chips of information. The rate at which the spread information is sent is referred to as the symbol rate (Rs), the ratio between the nominal symbol rate and chip rate is the spreading factor and represents the number of symbols sent per bit of information. The range of parameters which can be configured are given in the following tables.

| Spreading Factor (SF) | 5    | 6    | 7    | 8     | 9     | 10    | 11    |

|-----------------------|------|------|------|-------|-------|-------|-------|

| Chips/Symbol          | 32   | 64   | 128  | 256   | 512   | 1024  | 2048  |

| SNR (dB)              | -2.5 | -5.0 | -7.5 | -10.0 | -12.5 | -15.0 | -17.5 |

Table 2. NTR16CSW8 LoRa Mode Spreading Factors

Note that the spreading factor must be known in advance on both transmit and receive sides of the radio link as different spreading factors are orthogonal to each other. Note also the resulting signal to noise ratio (SNR) required at the receiver input. It is the capability to receive signals with negative SNR that increases the sensitivity, so link budget and range, of the LoRa receiver.

To further improve the robustness of the radio link NTR16CSW8 provides cyclic error coding with different coding rates. By using this coding scheme forward error detection and correction can be applied.

#### Differentiating Aspects of The NTR16CSW8 868MHz LoRa RF Transceiver Module

Main performance contributors of NTR16CSW8 are use of low ppm XTAL for high frequency stability and precision, use of harmonic filters for transmitter harmonic suppression and use of 868MHz SAW filter in RX path providing high selectivity which consequently providing high interference immunity and high sensitivity resulting in long range and exceptional bit error rate performance even in highly interfering environments with low SNR/SINR values.

NTR16CSW8 is optimized for +30dBm RF power output, PA settings should be arranged according to Section 5. Setting Modem, Transmitter & Receiver Parameters as in Table12B, for other PA configuration settings matching is not optimum and the RF power output may be different from intended usually at a higher current consumption.

#### 868MHz SAW Filter for High Selectivity and Interference Immunity

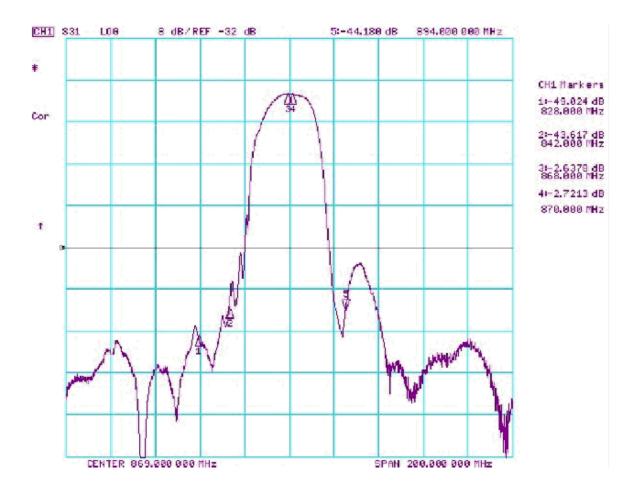

NTR16CSW8 includes a highly selective 868MHz SAW filter in RF front end in RX path for additional interference suppression. The characteristics of the SAW filter are given in Table 3 and Fig 4 below.

| Parameter        | Test Conditions | Min | Typical | Max | Unit |

|------------------|-----------------|-----|---------|-----|------|

| Center Frequency |                 | -   | 869     | -   | MHz  |

| 3-dB Bandwidth   |                 | -   | 11      | -   | MHz  |

|                  | 825 t0 828MHz   | 40  | 47      |     |      |

| Attenuation      | 835 to 842MHz   | 30  | 39      |     | dB   |

|                  | 891 to 894MHz   | 30  | 42      |     | иь   |

|                  | 910 to 913MHz   | 30  | 47      |     |      |

Table 3. NTR16CSW8 SAW Filter Characteristics

Fig.4 NTR16CSW8 RF Front End SAW Filter Frequency Response

# 2. NTR16CSW8 Technical Data

The tables below give the electrical specifications for the NTR16CSW8 868MHz LoRa RF Transceiver Module operating with LoRa and FSK/(G)FSK modulation.

| Symbol           | Parameter                       | Test Conditions                 | Min | Typical | Max | Unit  |

|------------------|---------------------------------|---------------------------------|-----|---------|-----|-------|

| $F_{op}$         | Operational Frequency/Band      | =                               | -   | 868     | -   | MHz   |

| c                | Concitivity FCV                 | @4.8kbps, BW-20kHz              | -   | -117    | -   | dBm   |

| $S_{RFIN-FSK}$   | Sensitivity-FSK                 | @0.6kbps, BW-4kHz               | -   | -124    |     | иын   |

| c                | Sensitivity-LoRa                | @SF9, BW-125kHz                 | -   | -128    | -   | dBm   |

| $S_{RFIN-LoRa}$  | Sensitivity-Lora                | @SF7, BW-500kHz                 | -   | -116    | -   | UDIII |

| $CCR_{FSK}$      | Co-channel Rejection-FSK        |                                 |     | -9      |     | dB    |

| $CCR_{LoRa}$     | Co-channel Rejection-LoRa       | @SF12                           |     | 19      |     | dB    |

| $ACR_{FSK}$      | Adjacent-channel Rejection-FSK  | +/-50kHz offset                 |     | 45      |     | dB    |

| $ACR_{LoRa}$     | Adjacent-channel Rejection-LoRa | +/-187kHz offset,SF-12          |     | 72      |     | dB    |

|                  | Blocking Immunity-FSK           | +/-1MHz offset                  |     | 68      |     |       |

| $BI_{FSK}$       | (4.8kbps, BW-20kHz)             | +/-2MHz offset                  |     | 70      |     | dB    |

|                  | (4.0kbps, BVV-20kHz)            | +/-10MHz offset                 |     | 80      |     |       |

|                  | Blocking Immunity-LoRa          | +/-1MHz offset                  |     | 88      |     |       |

| $BI_{LoRa}$      | (SF12, BW-125kHz)               | +/-2MHz offset                  |     | 90      |     | dB    |

|                  | (SI 12, BW-125K12)              | +/-10MHz offset                 |     | 99      |     |       |

| IMA              | Image Attenuation-LoRa          | with IQ calibration             |     | 54      |     | dB    |

| IIP <sub>3</sub> | Third Order Intercept Point     | Two tone test<br>(1MHz/1.96MHz) | -   | -5      | -   | dBm   |

Table 4. RF Radio Receiver /Receive Mode Characteristics

| Symbol      | Parameter                    | Test Conditions | Min | Typical | Max  | Unit |

|-------------|------------------------------|-----------------|-----|---------|------|------|

| $F_{op}$    | Operational Frequency/Band   | -               | -   | 868     | -    | MHz  |

| $P_{RFOUT}$ | Maximum Output Power         | -               | -   | +30     | -    | dBm  |

| $P_{RMP}$   | RF Output Power Ramping Time | Programmable    | 10  | -       | 3400 | usec |

Table 5. RF Radio Transmitter/Transmit Mode Characteristics

| Symbol      | Parameter                       | Test Conditions | Min   | Typical | Max  | Unit |

|-------------|---------------------------------|-----------------|-------|---------|------|------|

| $F_{step}$  | Synthesizer Frequency Step Size | -               | -     | 0.95    |      | Hz   |

| $SF_{LoRa}$ | Spreading Factor-LoRa           | Programmable    | 5     | -       | 12   | -    |

| $BR_{LoRa}$ | Bit Rate-LoRa                   | Programmable    | 0.018 | -       | 62.5 | kbps |

| $BW_{LoRa}$ | Bandwidth-LoRa                  | Programmable    | 7.8   |         | 500  | kHz  |

| $BR_{FSK}$  | Bit Rate-FSK                    | Programmable    | 0.6   | -       | 300  | kbps |

| $FDA_{FSK}$ | Frequency Deviation-FSK         | Programmable    | 0.6   | -       | 200  | kHz  |

Table 6. LoRa/FSK Modem and Frequency Synthesizer Characteristics

| Symbol         | Parameter                   | Test Conditions | Min     | Typical | Max     | Unit |

|----------------|-----------------------------|-----------------|---------|---------|---------|------|

| $V_{IH}$       | Input High Voltage          |                 | 0.7*VCC | -       | VCC+0.3 | V    |

| $V_{IL}$       | Input Low Voltage           |                 | -0.3    | -       | 0.3*VCC | V    |

| $V_{OH}$       | Output High Voltage         |                 | 0.9*VCC | -       | VCC     | V    |

| $V_{OL}$       | Output Low Voltage          |                 | 0       | -       | 0.1*VCC | V    |

| $V_{IL\_NRST}$ | Input High Voltage for NRST |                 | -0.3    | -       | 0.2*VCC | V    |

Table 7. Digital I/O Characteristics

| Symbol        | Parameter               | Test Conditions  | Min | Typical | Max | Unit |

|---------------|-------------------------|------------------|-----|---------|-----|------|

| $V_{cc}$      | Supply Voltage          | -                | -   | 5.0     | -   | V    |

| $I_{dd\_SLP}$ | Current–Sleep mode      |                  | -   | 600     | -   | nA   |

| $I_{dd\_TX}$  | Current–Transmit mode   | +30dBm RF Output | -   | 796     | -   | mA   |

| $I_{dd\_RX}$  | Current–Receive mode    |                  | -   | 4.6     | -   | mA   |

| $T_{op}$      | Operational Temperature | -                | -40 | -       | +85 | ٥C   |

**Table 8. Electrical Specifications**

#### **Absolute Maximum Ratings**

"Absolute maximum ratings" may cause permanent damage to the device and is a stress rating only, functional operation of the device under these conditions for extended periods may affect device reliability.

| Symbol    | Parameter               | Max      | Unit |

|-----------|-------------------------|----------|------|

| VDD       | Supply voltage          | 6.2      | V    |

| $T_{op}$  | Operational Temperature | -40~+85  | °C   |

| $T_{stg}$ | Storage Temperature     | -50~+150 | °C   |

| ESD       | ESD Rating              | 2(HBM)   | kV   |

**Table 9. Absolute Maximum Ratings**

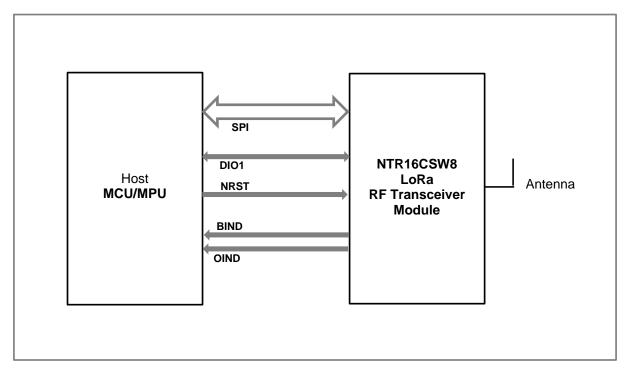

## 3. Interfacing NTR16CSW8 to Host Controller

The NTR16CSW8 is controlled via a serial SPI interface and a general-purpose input/output (DIO1) used for IRQ. The BIND (Busy Indicator) line is mandatory to ensure the host controller is ready to accept the commands. BIND is used as a busy signal indicating that the module is ready for new command only if this signal is low. When BIND is high, the host controller must wait until it goes down again before sending another command. Through SPI the application sends commands to the internal chip or accesses directly the data memory space.

#### Reset

A complete "factory reset" of the LLCC68 in module can be issued on request by toggling pin NRST of the NTR16CSW8. It will be automatically followed by the standard calibration procedure and any previous context will be lost. The pin should be held low for more typically 100µs for the Reset to happen.

#### **SPI Interface**

The SPI interface gives access to the configuration register via a synchronous full-duplex protocol corresponding to CPOL= 0 and CPHA = 0 and NTR16CSW8 behaves as slave. An address byte followed by a data byte is sent for a write access whereas an address byte is sent, and a read byte is received for the read access. The NSS pin goes low at the beginning of the frame and goes high after the data byte. MOSI is generated by the master on the falling edge of SCK and is sampled by the slave (i.e. this SPI interface) on the rising edge of SCK. MISO is generated by the slave on the falling edge of SCK. A transfer is always started by the NSS pin going low. MISO is high impedance when NSS is high. The SPI runs on the external SCK clock provided by the master.

#### **SPI Timing When the Transceiver Leaves Sleep Mode**

In Sleep mode and during the initialization phase, the busy signal mapped on BIND pin, is set high indicating to the host that the module is not able to accept a new command. Once the module is in STDBY\_RC mode, the busy signal goes low, and the host can start sending a command. This is also true for startup at battery insertion or after a hard reset.

One way for the module to leave Sleep mode is to wait for a falling edge of NSS. At falling edge, all necessary internal regulators are switched On; the module starts initialization before being able to accept first SPI command. This means that the delay between the falling edge of NSS and the first rising edge of SCK must take into account the wake-up sequence and the initialization.

Through the SPI interface, the host can issue commands to the module or access the data memory space to directly retrieve or write data. In normal operation, a reduced number of direct data write operations is required except when accessing the data buffer. The user interacts with the circuit through an API (instruction set).

The NTR16CSW8 module BIND pin indicates the status of the module and its ability (or not) to receive another command while internal processing occurs. Prior to executing one of the generic functions, it is thus necessary to check the status of BIND to make sure the module is in a state where it can process another function.

#### **Command Structure**

In case of a command that does not require any parameter, the host sends only the opcode (1 byte). In case of a command which requires one or several parameters, the opcode byte is followed immediately by parameter bytes with the NSS rising edge terminating the command.

#### **Transaction Termination**

The host terminates an SPI transaction with the rising NSS signal; the host does not explicitly send the command length as a parameter. The host must not raise NSS within the bytes of a transaction. If a transaction sends a command requiring parameters, all the parameters must be sent before rising NSS, if not the module will take some unknown value for the missing parameters.

More details about SPI interface, command structures, registers and FIFO can be found in LLCC68 Datasheet.

Fig.5 Interfacing NTR16CSW8 to MCU/MPU

## 4. Operational Modes

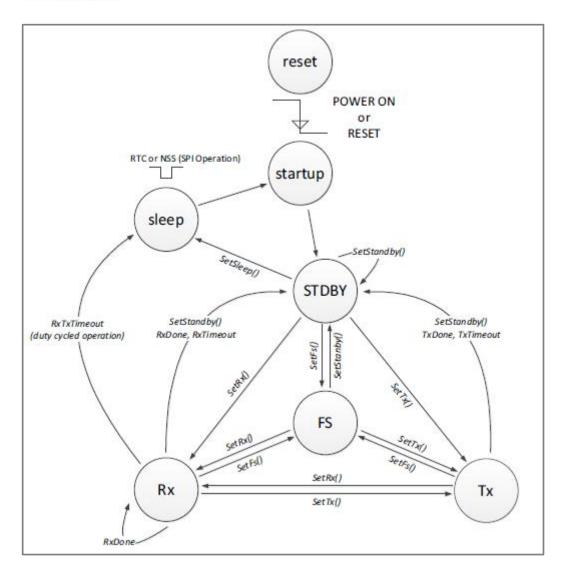

The NTR16CSW8 features six operating modes based on operating modes of LLCC68, each operating mode is explained in the following table and details of operational modes can be found in LLCC68 Datasheet.

| Operation Mode | Enabled Blocks                                                   |  |  |

|----------------|------------------------------------------------------------------|--|--|

| SLEEP          | Optional registers, backup regulator, RC64k oscillator, data RAM |  |  |

| STANDBY_RC     | Top regulator (LDO), RC13M oscillator                            |  |  |

| STANDBY_XOSC   | Top regulator (DC-DC or LDO), XOSC                               |  |  |

| FS             | All of the above + Frequency synthesizer at Tx frequency         |  |  |

| TX             | Frequency synthesizer and transmitter, Modem                     |  |  |

| RX             | Frequency synthesizer and receiver, Modem                        |  |  |

**Table 10. NTR16CSW8 Operational Modes**

#### Startup

At power-up or after a reset, the module goes into STARTUP state, the control being done by the sleep state machine operating at the battery voltage. The BIND pin is set to high indicating that the module is busy and cannot accept a command. When the digital voltage and RC clock become available, LLCC68 can boot up and the CPU takes control. At this stage the BIND line goes down and the device is ready to accept commands.

#### Calibration

The calibration procedure is automatically called in case of POR or via the calibration command. Parameters can be added to the calibrate command to identify which section of calibration should be repeated. The following blocks can be calibrated:

- RC64k using the 32 MHz XTAL as reference

- RC13M using the 32 MHz XTAL as reference

- PLL to select the proper VCO frequency and division ratio for any RF frequency

- RX ADC

- Image (RX mode with defined tone)

Once the calibration is finished, the chip enters STDBY\_RC mode.

#### **Image Calibration for Specific Frequency Bands**

Image calibration is done through the command *CalibrateImage(...)* for a given range of frequencies defined by the parameters *freq1* and *freq2*. Once performed, the calibration is valid for all frequencies between the two extremes used as parameters. Typically, the user can select the parameters *freq1* and *freq2* to cover any specific ISM band.

In case of POR or when the device is recovering from Sleep mode in cold start mode, the image calibration is performed as part of the initial calibration process and by default, the image calibration is made in the band 902-928MHz, therefore it should be repeated by requesting the device to perform a new image calibration for 868MHz frequency band by defining 863-870MHz band.

#### Sleep Mode

In this mode, most of the radio internal blocks are powered down or in low power mode and optionally the RC64k clock and the timer are running. The chip may enter this mode from STDBY\_RC and can leave the SLEEP mode if one of the following events occurs:

- NSS pin goes low in any case

- RTC timer generates an End-Of-Count (corresponding to Listen mode)

When the radio is in Sleep mode, the BIND pin is held high.

#### Standby (STDBY) Mode

In standby mode the host should configure the module before going to RX or TX modes. By default in this state, the system is clocked by the 13 MHz RC oscillator to reduce power consumption (in all other modes except SLEEP the XTAL is turned ON).

However, if the application is time critical, the XOSC block can be turned or left ON. XOSC or RC13M selection in standby mode is determined by mode parameter in the command *SetStandby(...)*.

The mode where only RC13M is used is called STDBY\_RC and the one with XOSC ON is called STDBY\_XOSC.

#### Frequency Synthesis (FS) Mode

In FS mode, PLL and related regulators are switched ON. The BIND goes low as soon as the PLL is locked or timed out. For debugging purposes the chip may be requested to remain in this mode by using the SetFs() command

#### Receive (RX) Mode

In RX mode, the RF front-end, RX ADC and the selected modem (LoRa or FSK) are turned ON. In RX mode the circuit can operate in different sub-modes:

- Continuous mode: the device remains in RX mode and waits for incoming packet reception until the host requests a different mode.

- Single mode: the device returns automatically to STDBY\_RC mode after packet reception,

- Single mode with timeout: the device returns automatically to STDBY\_RC mode after packet reception or after the selected timeout,

- Listen mode: the device alternate between Sleep and Rx mode until an IRQ is triggered.

In RX mode, BIND will go low as soon as the RX is enabled and ready to receive data.

The NTR16CSW8 can operate in Rx Boosted gain setup or in Rx power saving gain setup. In the Rx power saving gain, the radio will consume less power at a small cost in sensitivity. In Rx Boosted gain, the radio will consume more power to improve the sensitivity.

Fig.6 NTR16CSW8 Operational Modes

#### Transmit (TX) Mode

In TX mode, after enabling and ramping-up the Power Amplifier (PA), the contents of the data buffer are transmitted. The circuit can operate in different sub-modes: single mode or single with timeout mode.

In TX mode, BIND will go low as soon as the PA has ramped-up and transmission of preamble starts.

#### **PA Ramping**

The ramping of the PA can be selected while setting the output power by using the command SetTxParams(...). The PA ramp time can be selected to go from 10us up to 3.4ms.

## 5. Setting Modem, Transmitter & Receiver Parameters

The LLCC68 and consequently NTR16CSW8 contain different modems capable of handling LoRa and FSK modulations. LoRa and FSK are associated with their own frame and modem.

The user specifies the modem and frame type by using the command SetPacketType(...). This command specifies the frame used and consequently the modem implemented. This function is the first one to be called before going to Rx or Tx and before defining frequency, modulation and packet parameters.

#### **LoRa Modulation Technique and LoRa Parameters**

The LoRa modem uses spread spectrum modulation and forward error correction techniques to increase the range and robustness of radio communication links compared to traditional FSK based modulation. An important facet of the LoRa modem is its increased immunity to interference. The LoRa modem is capable of co-channel GMSK rejection of up to 16dB. This immunity to interference permits the simple coexistence of LoRa modulated systems either in bands of heavy spectral usage or in hybrid communication networks that use LoRa to extend range when legacy modulation schemes fail.

#### Modulation Parameter

It is possible to optimize the LoRa modulation for a given application, access is given to the designer to four critical design parameters, each one permitting a trade-off between the link budget, immunity to interference, spectral occupancy and nominal data rate. These parameters are:

- Modulation BandWidth (BW\_L)

- Spreading Factor (SF)

- Coding Rate (CR)

- Low Data Rate Optimization (LDRO)

These parameters are set using the command <code>SetModulationParams(...)</code> which must be called after <code>SetPacketType(...)</code>.

LoRa has its own packet engine that supports the LoRa PHY. More details about LoRa Modem, LoRa Modulation Paramaters, LoRa Packet Engine, LoRa Frame and LoRa Channel Activity Detection (CAD) can be found in LLCC68 Datasheet.

#### FSK/(G)FSK Modulation Technique and FSK/(G)FSK Parameters

The FSK modem can perform transmission and reception of 2-FSK modulated packets over a range of data rates from 0.6 kbps to 300 kbps. All parameters are set by using the command SetModulationParams(...). This function should be called only after defining the protocol. The bitrate setting is referenced to the crystal oscillator and provides a precise means of setting the bit rate (or equivalently chip) rate of the radio.

The LLCC68 and consequently NTR16CSW8 is designed for packet-based transmission. The packet controller block is responsible for assembly of the received data bit-stream into packets and their storage into the data buffer. It also performs the bit-stream decoding operations such as de-whitening & CRC-checks on the received bit-stream. On the transmit side, the packet handler can construct a packet and send it bit by bit to the modulator for transmission. It can whiten the payload and append the CRC-checksum to the end of the packet. The packet controller only works in half-duplex mode i.e. either in transmit or receive at a time. The packet controller is configured using the command SetPacketParams(...)

More details about FSK Modem, FSK Modulation Parameters, FSK Packet Format, FSK Frame and CRC use in FSK can be found in LLCC68 Datasheet.

#### RF Frequency, PA and TX Parameters

#### RF Frequency Setting

The command SetRfFrequency(...) is used to set the frequency of the RF frequency mode. The LSB of Freq is equal to the PLL step giving:

$$RF frequency = \frac{RF FreqxFXTAL}{2^{25}}$$

SetRfFrequency(...) defines the chip frequency in FS, TX and RX modes. In RX, the frequency is internally lowered to IF (250kHz by default).

| Byte           | 0           | 1-4          |

|----------------|-------------|--------------|

| Data from Host | Opcode=0x86 | RFfreq(31:0) |

**Table 11. RF Frequency Setting**

| RF Frequency | RFfreq(31:0) |

|--------------|--------------|

| 868MHz       | 0x36400000   |

| 869MHz       | 0x36500000   |

| 870MHz       | 0x36600000   |

| 867MHz       | 0x36300000   |

| 866MHz       | 0x36200000   |

**Table 11B. NTR16CSW8 Typical Frequency Settings**

#### PA Configuration

NTR16CSW8 PA matching hardware is optimal for +30dBm output power, therefore a sample set of PA settings are provided here.

paDutyCycle controls the duty cycle (conduction angle). The maximum output power, the power consumption, and the harmonics will drastically change with paDutyCycle. Changing the paDutyCycle will affect the distribution of the power in the harmonics and should be selected to work in conjunction with a given matching network. For implemented matching network, paDutyCycle can be selected as 0x04.

*hpMax* selects the size of the PA. The maximum output power can be reduced by reducing the value of *hpMax*. For implemented matching network, *hpMax* can be selected as 0x06.

deviceSel is reserved and has always the value 0x00.

paLut is reserved and has always the value 0x01.

### **PA Optimal Settings**

| Byte           | 0           | 1           | 2     | 3         | 4     |

|----------------|-------------|-------------|-------|-----------|-------|

| Data from Host | Opcode=0x98 | paDutyCycle | hpMax | deviceSel | paLut |

Table 12. PA Settings

| Byte           | 0                   | 1 | 2    | 3    | 4    |

|----------------|---------------------|---|------|------|------|

| Data from Host | om Host Opcode=0x98 |   | 0x06 | 0x00 | 0x01 |

Table 12B. NTR16CSW8 Recommended PA Settings

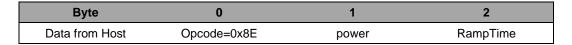

#### TX Parameters

SetTxParams command sets the TX output power by using the parameter *power* and the TX ramping time by using the parameter *RampTime*.

The power ramp time is defined by the parameter RampTime as defined in the following table

**Table 13. TX Settings**

| Byte           | 0           | 1    | 2    |

|----------------|-------------|------|------|

| Data from Host | Opcode=0x8E | 0x16 | 0x00 |

Table 13B. NTR16CSW8 Recommended TX Settings

| RampTime       | Value | RampTime(us) |

|----------------|-------|--------------|

| SET_RAMP_10U   | 0x00  | 10           |

| SET_RAMP_20U   | 0x01  | 20           |

| SET_RAMP_40U   | 0x02  | 40           |

| SET_RAMP_80U   | 0x03  | 80           |

| SET_RAMP_200U  | 0x04  | 200          |

| SET_RAMP_800U  | 0x05  | 800          |

| SET_RAMP_1700U | 0x06  | 1700         |

| SET_RAMP_3400U | 0x07  | 3400         |

**Table 14. PA Ramp Time Settings**

#### **Data Buffer**

The transceiver is equipped with a 256-byte RAM data buffer which is accessible in all modes except sleep mode. This RAM area is fully customizable by the user and allows access to either data for transmission or from the last packet reception.

#### Data Buffer in Receive Mode

In receive mode *RxBaseAddr* specifies the buffer offset in memory at which the received packet payload data will be written. The buffer offset of the last byte written in receive mode is then stored in *RxDataPointer* which is initialized to the value of *RxBaseAddr* at the beginning of the reception.

The pointer to the first byte of the last packet received and the packet length can be read with the command *GetRxbufferStatus()*. In single mode, *RxDataPointer* is automatically initialized to *RxBaseAddr* each time the transceiver enters Rx mode. In continuous mode the pointer is incremented starting from the previous position.

#### Data Buffer in Transmit Mode

Upon each transition to transmit mode *TxDataPointer* is initialized to *TxBaseAddr* and is incremented each time a byte is sent over the air. This operation stops once the number of bytes sent equals the payloadlength parameter as defined in the function *SetPacketParams(...)*.

#### Using the Data Buffer

Both, *RxBaseAddr* and *TxBaseAddr* are set using the command *SetBufferBaseAddresses(...)*. By default *RxBaseAddr* and *TxBaseAddr* are initialized at address 0x00.

Due to the contiguous nature of the data buffer, the base addresses for Tx and Rx are fully configurable across the 256-byte memory area. Each pointer can be set independently anywhere within the buffer. To exploit the maximum data buffer size in transmit or receive mode, the whole data buffer can be used in each mode by setting the base addresses *TxBaseAddr* and *RxBaseAddr* at the bottom of the memory (0x00).

The data buffer is cleared when the device is put into Sleep mode (implying no access). The data is retained in all other modes of operation.

#### Note:

All the received data will be written to the data buffer even if the CRC is invalid, permitting user-defined post processing of corrupted data. When receiving, if the packet size exceeds the buffer memory allocated for the Rx, it will overwrite the transmit portion of the data buffer.

More details about Data Buffer, Use of Data Buffer, Writing to and Reading from Buffer and Registers can be found in LLCC68 Datasheet.

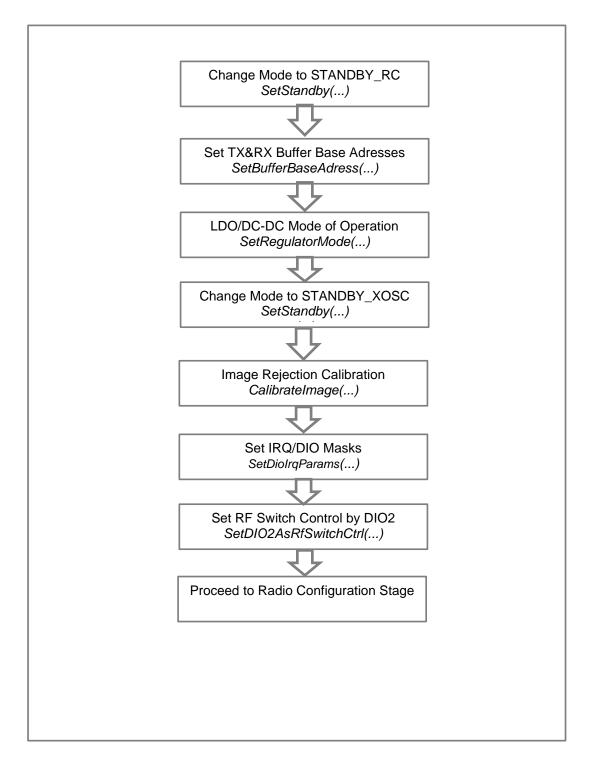

## 6. Module Aspects To Consider for User Application

NTR16CSW8 LoRa RF Transceiver module uses low ppm XTAL for high frequency stability and also an RF switch for TX and RX path switching in transmit and receive modes respectively. The user application code should contain proper settings for DC-DC or LDO Only mode of regulator operation, XTAL use, RF switch use and proper calibration as detailed in following sections.

#### **LDO Only or DC-DC Mode of Operation**

In LLCC68 two forms of voltage regulation (DC-DC buck converter or linear LDO regulator) are available, the linear LDO regulator is always present in all modes but the transceiver will use DC-DC when selected. By default, only the LDO is used. SetRegulatorMode(...) function specifies if DC-DC or LDO is used for power regulation. The user can specify the use of DC-DC by using the command SetRegulatorMode(...). This operation must be carried out in STDBY\_RC mode only. The regulation mode is defined by parameter regModeParam.

| Byte           | 0           | 1                                              |

|----------------|-------------|------------------------------------------------|

| Data from Host | Opcode=0x96 | regModeParam<br>0: Only LDO used for all modes |

|                |             | 1: DC_DC+LDO for STBY_XOSC,FS, RX and TX       |

**Table 15. Regulator Mode Selection**

Hardware implementation of the NTR16CSW8 allows using LDO only or LDO plus DC-DC mode of operations.

#### Image Calibration for 868MHz Frequency Band

In case of POR or when the device is recovering from Sleep mode in cold start mode, the image calibration is performed as part of the initial calibration process and for optimal image rejection in the band 902 - 928 MHz.

Image calibration is done through the command *CalibrateImage(...)* for a given range of frequencies defined by the parameters *freq1* and *freq2*. Once performed, the calibration is valid for all frequencies between the two extremes used as parameters. Typically, the user can select the parameters *freq1* and *freq2* to cover any specific ISM band.

| Byte           | 0           | 1     | 2     |

|----------------|-------------|-------|-------|

| Data from Host | Opcode=0x98 | freq1 | freq2 |

Table 18. Image Calibration for 868MHz frequency band

By default, the image calibration is made in the band 902 - 928 MHz, therefore it should be repeated by requesting the device to perform a new image calibration for 868MHz frequency band by defining 863-870MHz band.

| Frequency Band | freq1 | freq2 |

|----------------|-------|-------|

| 863MHz-870MHz  | 0xD7  | 0xDB  |

**Table 19. Image Calibration Frequencies**

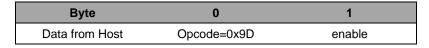

#### Use of RF Switch (controlled by DIO2)

NTR16CSW8 uses an RF switch to activate/deactivate TX and RX paths in transmit and receive modes respectively, and RF switch used is controlled by DIO2 multifunction I/O pin of LLCC68, therefore the user application should take use of DIO2 into account detailed as follows.

DIO2 should be configured to drive the RF switch through the use of the command SetDio2AsRfSwitchCtrl(...). In this mode, DIO2 will be at a logical 1 during Tx and at a logical 0 in any other mode. DIO2 will be asserted high a few microseconds before the ramp-up of the PA and will be set to zero after the ramp-down of the PA.

Table 20. DIO2 RF Switch Configuration

The enable byte definition is given as follows:

| Enable | Description                                                                                                                                      |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00   | DIO2 is free to be used as an IRQ                                                                                                                |

| 0x01   | DIO2 is selected to be used to control an RF switch. In this case: DIO2 = 0 in SLEEP, STDBY_RX, STDBY_XOSC, FS and RX modes, DIO2 = 1 in TX mode |

**Table 21. DIO2 Options**

#### Note:

For proper operation of the NTR16CSW8, the DIO2 should be configured accordingly by enabling with 0x01 parameter.

#### Application Code Structure and Issuing Commands in the Right Order

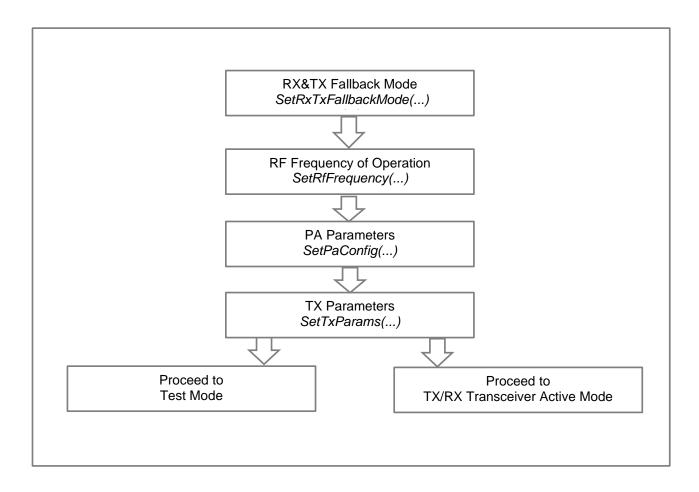

NTR16CSW8 hardware is suitable for LDO only or DC-DC regulator mode of operation, includes an RF switch controlled by DIO2 of LLCC68, therefore related IRQ/DIO mask settings, RF switch settings should be configured, transmit and receive buffer base addresses should be defined and a calibration should be performed before radio configuration and operation.

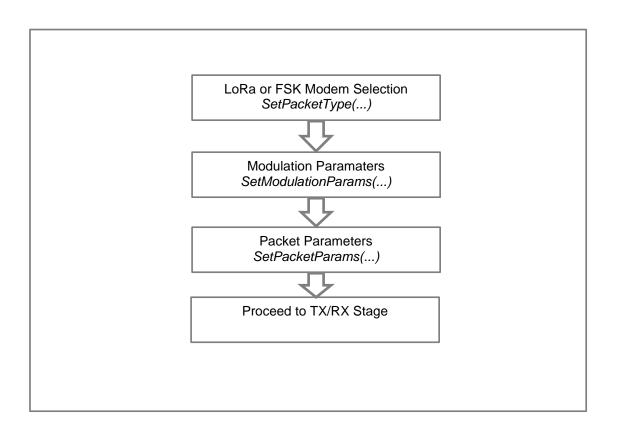

Fig.7 Configuration and Settings - Standby Mode

Most of the commands can be sent in any order except for the radio configuration commands which will set the radio in the proper operating mode.

It is mandatory to set the radio protocol using the command SetPacketType(...) as a first step before issuing any other radio configuration commands.

In a second step, the user should define the modulation parameter according to the chosen protocol with the command *SetModulationParams(...)*.

Finally, the user should then select the packet format with the command SetPacketParams(...).

Note: If this order is not respected, the behavior of the device could be unexpected

Fig.8 Configuration and Settings - Modem Selection, Modulation and Packet Parameters

Fig.9 Configuration and Settings – RF Frequency, PA and TX/RX Parameters

# 7. Drawings

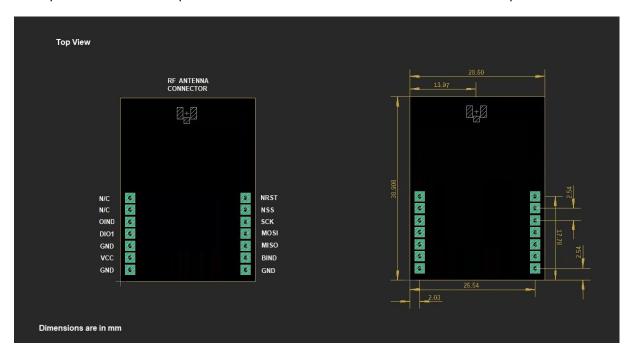

Figure.10 depicts a description of connector pinout and module dimensions for NTR16CSW8. A detailed description of the individual pins can be found in Table 22 Connector and Pin Descriptions.

Fig.10 NTR16CSW8 Pin and Size Diagram

| CONNECTORS  |              |                                |  |

|-------------|--------------|--------------------------------|--|

| Pin No      | Pin Name     | Pin Function                   |  |

| CA          | ANT          | RF Output/Antenna              |  |

| J1-Connecte | or           |                                |  |

| J1-1        | N/C          | No Connection (Internally GND) |  |

| J1-2        | N/C          | No Connection (Internally GND) |  |

| J1-3        | OIND         | Operation Indicator            |  |

| J1-4        | DIO1         | Data I/O                       |  |

| J1-5        | GND          | 0V, Ground                     |  |

| J1-6        | VCC          | +Supply Voltage                |  |

| J1-7        | GND          | 0V, Ground                     |  |

| J2-Connecto | J2-Connector |                                |  |

| J2-1        | NRST         | Reset                          |  |

| J2-2        | NSS          | SPI chip select                |  |

| J2-3        | SCK          | SPI clock                      |  |

| J2-4        | MOSI         | SPI MOSI                       |  |

| J2-5        | MISO         | SPI MISO                       |  |

| J2-6        | BIND         | Busy Indicator                 |  |

| J2-7        | GND          | 0V, Ground                     |  |

Table 22. Connector and Pin Descriptions (NTR16CSW8)

# 8. Ordering Information

| Order Code | Description                                                                | MOQ |

|------------|----------------------------------------------------------------------------|-----|

| NTR16CSW8  | NTR16CSW8 868MHz/+30dBm LoRa RF Transceiver Module (with SMA RF Connector) | 10  |

Table 23. NTR16CSW8 Ordering Info

# **Revision History**

| Date            | Revision | Modifications   |

|-----------------|----------|-----------------|

| August 12, 2024 | 1.1      | Initial release |

# References

- 1) Semtech LLCC68 Datasheet https://www.egn-elektronik.com.tr/EN/Datasheets/LLCC68.pdf

- 2) LLCC68 Drivers <a href="https://github.com/Lora-net/llcc68">https://github.com/Lora-net/llcc68</a> driver